GlobalFoundries prepares Tri-Gate competitor

July 12, 2011 | 12:46

Companies: #global-foundries #globalfoundries

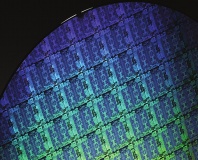

In a recent briefing, Global Foundries revealed to bit-tech that it's already working on a competitor to Intel's recently-announced 3D Tri-Gate transistors.

When asked whether GlobalFoundries was developing a similar product to Intel's new 3D transistors, the company's VP of technology and integration engineering, Dirk Wristers, stated that the company did have ‘3D activity.’

In addition to this, Wristers also took the opportunity to flesh out GlobalFoundries' production process roadmap. As reported previously, the firm will use the gate-first method of semiconductor production at the 28nm node, but will move to gate-last production for its 20nm process in 2013.

In case you're unfamiliar with the latest CPU manufacturing jargon, gate-last and gate-first refer to the point at which a transistor's gate is put onto a CPU-production wafer.

Previously, CPU transistors featured a silicon gate and a silicon dioxide insulator. However, in order to combat the problems with current leakage as silicon gets thinner, most fabrication firms have now replaced the silicon-based parts with a metal gate and a high-k insulator made from a material such as Hafnium. This means that a fabrication company has to choose whether the metal gate electrode is dropped onto the wafer before or after the high-temperature heating process.

When pushed about the yield implications of gate-first production, Wristers stated that ‘gate-first is the right option [for Global Foundries], and is not an issue at this point.’

He also stated that gate-first production saves around 10-20 per cent space at the 28nm node over the gate-last process used by both Intel and TSMC. According to Wristers, this enables ‘gate-first to offer superior value to gate-last.'

Despite being bullish on the use of the gate-first production, though, Wristers claimed that GlobalFoundries' 20nm gate-last production process should enable a 50 per cent reduction in the size of SRAM and logic circuits, when compared to 28nm production, and that the company had needed to innovate in its approach to 20nm production. This was forced, he explained, by the fact that the ‘density and scaling benefits of gate-first high-K metal gate no longer apply because of patterning-dominated lithography restrictions.’

In addition to this, Wristers also confirmed that GlobalFoundries' R&D into 14nm transistors is ‘well underway’. Wristers confirmed that Global Foundries is exploring a number of novel approaches to this production node, including such as a Multi-gate FinFET transistor structure and a number of source mask optimisations to improve pattern fidelity.

Are you excited by the steady march of semiconductor production technology? How small can we make silicon transistors before they become unmanageable? Let us know your thoughts in the forums.

When asked whether GlobalFoundries was developing a similar product to Intel's new 3D transistors, the company's VP of technology and integration engineering, Dirk Wristers, stated that the company did have ‘3D activity.’

In addition to this, Wristers also took the opportunity to flesh out GlobalFoundries' production process roadmap. As reported previously, the firm will use the gate-first method of semiconductor production at the 28nm node, but will move to gate-last production for its 20nm process in 2013.

In case you're unfamiliar with the latest CPU manufacturing jargon, gate-last and gate-first refer to the point at which a transistor's gate is put onto a CPU-production wafer.

Previously, CPU transistors featured a silicon gate and a silicon dioxide insulator. However, in order to combat the problems with current leakage as silicon gets thinner, most fabrication firms have now replaced the silicon-based parts with a metal gate and a high-k insulator made from a material such as Hafnium. This means that a fabrication company has to choose whether the metal gate electrode is dropped onto the wafer before or after the high-temperature heating process.

When pushed about the yield implications of gate-first production, Wristers stated that ‘gate-first is the right option [for Global Foundries], and is not an issue at this point.’

He also stated that gate-first production saves around 10-20 per cent space at the 28nm node over the gate-last process used by both Intel and TSMC. According to Wristers, this enables ‘gate-first to offer superior value to gate-last.'

Despite being bullish on the use of the gate-first production, though, Wristers claimed that GlobalFoundries' 20nm gate-last production process should enable a 50 per cent reduction in the size of SRAM and logic circuits, when compared to 28nm production, and that the company had needed to innovate in its approach to 20nm production. This was forced, he explained, by the fact that the ‘density and scaling benefits of gate-first high-K metal gate no longer apply because of patterning-dominated lithography restrictions.’

In addition to this, Wristers also confirmed that GlobalFoundries' R&D into 14nm transistors is ‘well underway’. Wristers confirmed that Global Foundries is exploring a number of novel approaches to this production node, including such as a Multi-gate FinFET transistor structure and a number of source mask optimisations to improve pattern fidelity.

Are you excited by the steady march of semiconductor production technology? How small can we make silicon transistors before they become unmanageable? Let us know your thoughts in the forums.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.