Memory specialist Micron has won an award for its Hybrid Memory Cube technology, a prototype system which promises to boost massively improve DRAM performance while dropping the power draw drastically over current generation hardware.

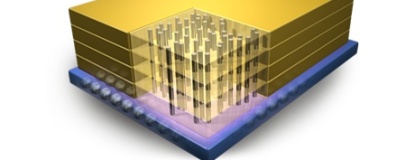

Based on through-silicon via technology - vertical conduits that allow components to be connected in a three dimensional mesh, in a way not dissimilar to Intel's tri-gate transistor technology - Micron's Hybrid Memory Cubes promise significantly improved performance over existing two-dimensional memory structures: current prototypes push 128GB/s, compared to peak throughput of around 12.8GB/s obtainable via commercial DDR3 DRAM implementations.

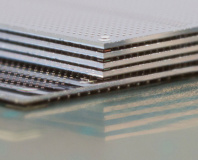

Micron's HMC isn't just about improving performance, however: prototype implementations of the technology boast a 70 per cent reduction in power draw during data transfer while reducing the footprint to one-tenth that of traditional two-dimensional memory; as a result, the technology is turning heads in the world of ultra-mobile computing and embedded systems.

Sadly, the technology isn't destined for desktops and smartphones just yet: due to the heightened cost of HMC chips compared to traditional DRAM, the company is concentrating its efforts in large-scale networking and high-performance computing (HPC) markets. Once production costs have lowered, industrial automation will be next before the consumer markets finally get their hands on the technology.

That somewhat lengthy roadmap to affordable implementations hasn't stopped The Linley Group, a microprocessor and semiconductor industry analysis organisation, awarding the company Best New Technology in its 2011 awards. 'Hybrid Memory Cubes promise greater density, lower latency, higher bandwidth, and better power efficiency per bit compared with conventional memories,' explained Tom R. Halfhill, a senior analyst at The Linley Group and one of those responsible for the award. 'Early benchmarks show a memory cube blasting data 12 times faster than DDR3-1333 SDRAM while using only about 10 percent of the power.'

'With so many other great innovations out there, we're especially honored to receive this prestigious award from The Linley Group. This world-class recognition is a reflection on the team that is working to match processors with memory and break down the memory wall by bringing the Hybrid Memory Cube to the market," added Brian Shirley, vice president for Micron’s DRAM Solutions Group, at the award ceremony. 'Special thanks to the Micron engineers who've designed this breakthrough architecture, and to our esteemed colleagues in the industry who are helping to expedite the specifications and manufacturing for this revolutionary technology.'

Wondering what chips will be turned three-dimensional next, or just impatient to get your hands on consumer-grade implementations? Share your thoughts over in the forums.

Based on through-silicon via technology - vertical conduits that allow components to be connected in a three dimensional mesh, in a way not dissimilar to Intel's tri-gate transistor technology - Micron's Hybrid Memory Cubes promise significantly improved performance over existing two-dimensional memory structures: current prototypes push 128GB/s, compared to peak throughput of around 12.8GB/s obtainable via commercial DDR3 DRAM implementations.

Micron's HMC isn't just about improving performance, however: prototype implementations of the technology boast a 70 per cent reduction in power draw during data transfer while reducing the footprint to one-tenth that of traditional two-dimensional memory; as a result, the technology is turning heads in the world of ultra-mobile computing and embedded systems.

Sadly, the technology isn't destined for desktops and smartphones just yet: due to the heightened cost of HMC chips compared to traditional DRAM, the company is concentrating its efforts in large-scale networking and high-performance computing (HPC) markets. Once production costs have lowered, industrial automation will be next before the consumer markets finally get their hands on the technology.

That somewhat lengthy roadmap to affordable implementations hasn't stopped The Linley Group, a microprocessor and semiconductor industry analysis organisation, awarding the company Best New Technology in its 2011 awards. 'Hybrid Memory Cubes promise greater density, lower latency, higher bandwidth, and better power efficiency per bit compared with conventional memories,' explained Tom R. Halfhill, a senior analyst at The Linley Group and one of those responsible for the award. 'Early benchmarks show a memory cube blasting data 12 times faster than DDR3-1333 SDRAM while using only about 10 percent of the power.'

'With so many other great innovations out there, we're especially honored to receive this prestigious award from The Linley Group. This world-class recognition is a reflection on the team that is working to match processors with memory and break down the memory wall by bringing the Hybrid Memory Cube to the market," added Brian Shirley, vice president for Micron’s DRAM Solutions Group, at the award ceremony. 'Special thanks to the Micron engineers who've designed this breakthrough architecture, and to our esteemed colleagues in the industry who are helping to expedite the specifications and manufacturing for this revolutionary technology.'

Wondering what chips will be turned three-dimensional next, or just impatient to get your hands on consumer-grade implementations? Share your thoughts over in the forums.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.