Intel has detailed what makes its new Xeon Processor Scalable - and, by definition, its latest high-end desktop (HEDT) processors designs - just so scalable: a revised on-chip interconnect built around a mesh layout.

Announced back in May, Intel described the Xeon Processor Scalable range as having been 're-architected from the ground up' and representing 'a major architecture leap forward in processor architecture and platform advancements.' While the company promised a near-quadrupling in scalability for virtualised workloads and a new tiered ranking system based on Bronze, Silver, Gold, and Platinum stock keeping unit (SKU) levels, it was somewhat quieter on exactly what had changed internally.

Now, Intel chip architect Akhilesh Kumar has penned a blog post describing at least one of the architecture changes: a mesh-style interconnect platform. 'The task of adding more cores and interconnecting them to create a multi-core data centre processor may sound simple, but the interconnects between CPU cores, memory hierarchy, and I/O subsystems provide critical pathways among these subsystems necessitating thoughtful architecture,' explains Kumar in his post. 'These interconnects are like a well-designed highway with the right number of lanes and ramps at critical places to allow traffic to flow smoothly rather than letting people and goods sit idle on the road without being productive.

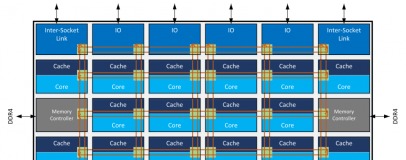

'Intel has applied its experience and innovation in developing a new architecture for the upcoming Intel Xeon Scalable processors to provide a scalable foundation for the modern data centre. This new architecture delivers a new way of interconnecting on-chip components to improve the efficiency and scalability of multi-core processors. The Intel Xeon Scalable processors implement an innovative “mesh” on-chip interconnect topology that delivers low latency and high bandwidth among cores, memory, and I/O controllers,' Kumar adds. 'Cores, on-chip cache banks, memory controllers, and I/O controllers are organised in rows and columns, with wires and switches connecting them at each intersection to allow for turns. By providing a more direct path than the prior ring architectures and many more pathways to eliminate bottlenecks, the mesh can operate at a lower frequency and voltage and can still deliver very high bandwidth and low latency. This results in improved performance and greater energy efficiency similar to a well-designed highway system that lets traffic flow at the optimal speed without congestion.

'In addition to improving the connectivity and topology of the on-chip interconnect, the Intel® Xeon® Scalable processors also implement a modular architecture with scalable resources for accessing on-chip cache, memory, IO, and remote CPUs. These resources are distributed throughout the chip so “hot-spots” or other subsystem resource constraints are minimised. This modular and distributed aspect of the architecture allows available resources to scale as the number of processor cores increase.'

In short, the company is opting for a semi-tile-based layout of cores and cache similar to that implemented in 2009 by tile-processor specialist Tilera for a 100-core chip design. Its iMesh-based Tile processor family proved popular for networking and high-throughput tasks, and the company was acquired by EZchip Semiconductor in 2014.

While the company's new mesh architecture - which will go up against AMD's rival Infinity Fabric, as implemented in the company's Ryzen architecture - was originally designed for the Skylake-based Xeon Processor Scalable family, it will also trickle down to the company's high-end desktop (HEDT) many-core products including the Skylake-X range.

Announced back in May, Intel described the Xeon Processor Scalable range as having been 're-architected from the ground up' and representing 'a major architecture leap forward in processor architecture and platform advancements.' While the company promised a near-quadrupling in scalability for virtualised workloads and a new tiered ranking system based on Bronze, Silver, Gold, and Platinum stock keeping unit (SKU) levels, it was somewhat quieter on exactly what had changed internally.

Now, Intel chip architect Akhilesh Kumar has penned a blog post describing at least one of the architecture changes: a mesh-style interconnect platform. 'The task of adding more cores and interconnecting them to create a multi-core data centre processor may sound simple, but the interconnects between CPU cores, memory hierarchy, and I/O subsystems provide critical pathways among these subsystems necessitating thoughtful architecture,' explains Kumar in his post. 'These interconnects are like a well-designed highway with the right number of lanes and ramps at critical places to allow traffic to flow smoothly rather than letting people and goods sit idle on the road without being productive.

'Intel has applied its experience and innovation in developing a new architecture for the upcoming Intel Xeon Scalable processors to provide a scalable foundation for the modern data centre. This new architecture delivers a new way of interconnecting on-chip components to improve the efficiency and scalability of multi-core processors. The Intel Xeon Scalable processors implement an innovative “mesh” on-chip interconnect topology that delivers low latency and high bandwidth among cores, memory, and I/O controllers,' Kumar adds. 'Cores, on-chip cache banks, memory controllers, and I/O controllers are organised in rows and columns, with wires and switches connecting them at each intersection to allow for turns. By providing a more direct path than the prior ring architectures and many more pathways to eliminate bottlenecks, the mesh can operate at a lower frequency and voltage and can still deliver very high bandwidth and low latency. This results in improved performance and greater energy efficiency similar to a well-designed highway system that lets traffic flow at the optimal speed without congestion.

'In addition to improving the connectivity and topology of the on-chip interconnect, the Intel® Xeon® Scalable processors also implement a modular architecture with scalable resources for accessing on-chip cache, memory, IO, and remote CPUs. These resources are distributed throughout the chip so “hot-spots” or other subsystem resource constraints are minimised. This modular and distributed aspect of the architecture allows available resources to scale as the number of processor cores increase.'

In short, the company is opting for a semi-tile-based layout of cores and cache similar to that implemented in 2009 by tile-processor specialist Tilera for a 100-core chip design. Its iMesh-based Tile processor family proved popular for networking and high-throughput tasks, and the company was acquired by EZchip Semiconductor in 2014.

While the company's new mesh architecture - which will go up against AMD's rival Infinity Fabric, as implemented in the company's Ryzen architecture - was originally designed for the Skylake-based Xeon Processor Scalable family, it will also trickle down to the company's high-end desktop (HEDT) many-core products including the Skylake-X range.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.