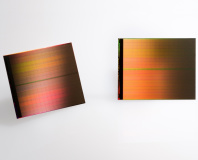

Memory specialist Micron claims to have solved the four-bank activation window timing challenge in dynamic RAM (DRAM) with an immediate 18 per cent boost in performance for DDR3-2133 modules.

The four-bank activation window (tFAW) is one of a number of timing parameters in modern double-data rate (DDR) DRAM which, the company claims, can restrict performance in high-bandwidth environments. Typically, this value is set to 35ns - meaning that to activate ten banks takes three tFAW cycles, or 105ns.

The delay in bank activation causes a performance bottleneck problem in high-performance, high operations per second (OPS) scenarios, particularly in the network industry where data must be shuffled to and from RAM extremely quickly to keep up with the ever-increasing speed of network connections. As a result, Micron has worked with Broadcom to develop DRAM modules with a significantly reduced tFAW cycle of just 30ns.

According to the pair's testing, the new modules offer an improvement in operations per second of 18 per cent - a not-insignificant gain in OPS-hungry devices. The first such device to feature Micron's new high-speed tFAW DRAM modules will be Broadcom's BCM88030 network processing unit (NPU) with a claimed 200Gb/s wire-speed layer two, IPv4 and IPv6 lookup capability.

'OEMs today continue to tackle the challenge of an ever-increasing volume, velocity and variety of data,' claimed Robert Feurle, vice president of DRAM marketing at Micron, at the announcement. 'We are delighted to be working with Broadcom to validate a solution that helps alleviate the throughput challenge for our mutual customers.'

Although the modules have been developed in partnership with Broadcom, Micron is offering the parts to all customers in 2GB and 4GB modules. Initially, the target market will be OPS-heavy network processing devices, but we can expect to see the technology coming to more consumer-facing devices in the near future as well.

The four-bank activation window (tFAW) is one of a number of timing parameters in modern double-data rate (DDR) DRAM which, the company claims, can restrict performance in high-bandwidth environments. Typically, this value is set to 35ns - meaning that to activate ten banks takes three tFAW cycles, or 105ns.

The delay in bank activation causes a performance bottleneck problem in high-performance, high operations per second (OPS) scenarios, particularly in the network industry where data must be shuffled to and from RAM extremely quickly to keep up with the ever-increasing speed of network connections. As a result, Micron has worked with Broadcom to develop DRAM modules with a significantly reduced tFAW cycle of just 30ns.

According to the pair's testing, the new modules offer an improvement in operations per second of 18 per cent - a not-insignificant gain in OPS-hungry devices. The first such device to feature Micron's new high-speed tFAW DRAM modules will be Broadcom's BCM88030 network processing unit (NPU) with a claimed 200Gb/s wire-speed layer two, IPv4 and IPv6 lookup capability.

'OEMs today continue to tackle the challenge of an ever-increasing volume, velocity and variety of data,' claimed Robert Feurle, vice president of DRAM marketing at Micron, at the announcement. 'We are delighted to be working with Broadcom to validate a solution that helps alleviate the throughput challenge for our mutual customers.'

Although the modules have been developed in partnership with Broadcom, Micron is offering the parts to all customers in 2GB and 4GB modules. Initially, the target market will be OPS-heavy network processing devices, but we can expect to see the technology coming to more consumer-facing devices in the near future as well.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.