Kingston vs OCZ DDR2-800MHz Memory

February 23, 2007 | 16:18

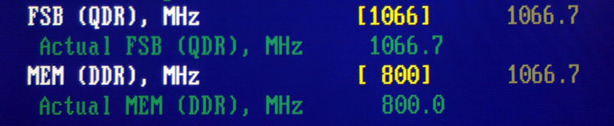

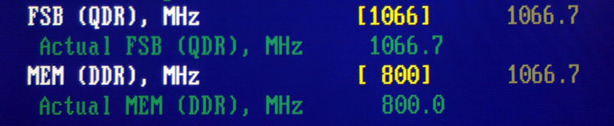

Memory modules are an inevitable and sometimes confusing choice in a computer purchase, even more so when overclocking. From our own internal testing, we found that the optimal memory speed for Intel Core 2 Duo processors is PC6400 or DDR2 800MHz and thus, we feel that this is the minimum memory speed you should aim for when upgrading to Core 2. However, JEDEC, the Joint Electron Device Engineering Council, being the official authority in all things memory has only rated the maximum DDR2 memory speed as PC5400, 667MHz at 5-5-5-15-2T.

Anything faster than this is over and above “official” specifications. Obviously, memory companies want to sell you more, so faster memory has inevitably been developed and marketed at a premium. Now DDR2 speeds have almost scaled into DDR3 territory, with speeds in excess of 1200MHz. Taking this into account, we were interested in finding out if relatively middle of the road DDR2-800 memory is enough to cater for most of your Core 2 overclocking endeavours.

Memory still basically internally made up of columns, rows and banks. These have separate addresses, and the time it takes to look at one, move from one to the other, or charge the memory for its next use is all controlled via the memory timings. These have to be taken into account to determine how your memory performs, with lower numbers meaning less time being taken so things get done faster. Each of the timings is represented in clock cycles: so setting lower means less time, but higher clock speeds mean there are more clock cycles available. It’s a balance between the two. A typical set of DDR2 memory timings like 5-5-5-15-2T, translates to the following:

CAS (tCL): Column Address Strobe is where the selected column is read and sent to data. This used to be a major number back in the SDR/DDR days as it depicted a large percentage of memory performance. However, DDR2 is less CAS sensitive and memory rated “CL5” or “CAS5” usually means 4-4-4-x or 5-5-5-x across the timings.

CAS (tCL): Column Address Strobe is where the selected column is read and sent to data. This used to be a major number back in the SDR/DDR days as it depicted a large percentage of memory performance. However, DDR2 is less CAS sensitive and memory rated “CL5” or “CAS5” usually means 4-4-4-x or 5-5-5-x across the timings.

tRCD: RAS to CAS Delay is the time delay in clock cycles for the earliest time to issue a READ to WRITE command after a bank was previously active.

tRP: Row Precharge is the time used for precharging the memory before it’s addressed, or minimum time used to wait for a command after precharging. Memory doesn’t wait for a read/write command before recharging, but there needs to be enough time for the capacitance to charge in the memory in order for it to remain stable once being read / written (this is regardless of the refresh cycle). Usually increasing the voltage can help, but at the cost of the life to the sensitive modules as well as RF crosstalk between wires. By optimising this timing, the memory spends less time waiting for the precharge to finish before the memory can be read / written.

tRAS: The Row Address Strobe is the row equivalent of CAS but generally more sensitive to change than the other values. The number uses increases in excess of that of the other values when it comes to overclocking and stability.

Command Rate: This is the rate at which commands are issued to the memory from the chipset. Setting too fast means that commands are either issued too quickly and the memory can’t execute them fast enough, or, there is still capacitance in the wiring from the previous command when the next is issued, causing errors. 1T and 2T are the only options to consider, so it’s worth trying at 1T first. However this is hard on both your memory and motherboard, and a poorly engineered product or BIOS will not accept the tighter 1T timing.

Finally, a fifth number is occasionally portrayed as tRC: Row Cycle Time. This is usually a large number and the minimum time an ACTIVE command can be issued to the same bank and should be at least tRAS + tRP.

Anything faster than this is over and above “official” specifications. Obviously, memory companies want to sell you more, so faster memory has inevitably been developed and marketed at a premium. Now DDR2 speeds have almost scaled into DDR3 territory, with speeds in excess of 1200MHz. Taking this into account, we were interested in finding out if relatively middle of the road DDR2-800 memory is enough to cater for most of your Core 2 overclocking endeavours.

What do these timings mean?

We discussed memory jargon in depth when we tried to establish if more memory made for a better gaming experience back in the days when Athlon 64 was still on socket 939 and only had Intel's Netburst-based processors to compete with; here's a quick refresh for the Core 2 / DDR2 era.Memory still basically internally made up of columns, rows and banks. These have separate addresses, and the time it takes to look at one, move from one to the other, or charge the memory for its next use is all controlled via the memory timings. These have to be taken into account to determine how your memory performs, with lower numbers meaning less time being taken so things get done faster. Each of the timings is represented in clock cycles: so setting lower means less time, but higher clock speeds mean there are more clock cycles available. It’s a balance between the two. A typical set of DDR2 memory timings like 5-5-5-15-2T, translates to the following:

tRCD: RAS to CAS Delay is the time delay in clock cycles for the earliest time to issue a READ to WRITE command after a bank was previously active.

tRP: Row Precharge is the time used for precharging the memory before it’s addressed, or minimum time used to wait for a command after precharging. Memory doesn’t wait for a read/write command before recharging, but there needs to be enough time for the capacitance to charge in the memory in order for it to remain stable once being read / written (this is regardless of the refresh cycle). Usually increasing the voltage can help, but at the cost of the life to the sensitive modules as well as RF crosstalk between wires. By optimising this timing, the memory spends less time waiting for the precharge to finish before the memory can be read / written.

tRAS: The Row Address Strobe is the row equivalent of CAS but generally more sensitive to change than the other values. The number uses increases in excess of that of the other values when it comes to overclocking and stability.

Command Rate: This is the rate at which commands are issued to the memory from the chipset. Setting too fast means that commands are either issued too quickly and the memory can’t execute them fast enough, or, there is still capacitance in the wiring from the previous command when the next is issued, causing errors. 1T and 2T are the only options to consider, so it’s worth trying at 1T first. However this is hard on both your memory and motherboard, and a poorly engineered product or BIOS will not accept the tighter 1T timing.

Finally, a fifth number is occasionally portrayed as tRC: Row Cycle Time. This is usually a large number and the minimum time an ACTIVE command can be issued to the same bank and should be at least tRAS + tRP.

What does this translate to in the real world?

We’ve previously shown that Core 2 Duo processors are particularly susceptible to changes in memory timings, and loosening them causes a greater loss of bandwidth than overclocking does. Thus, the ability for PC6400 modules to do very low latency by increasing the voltage is highly sought after.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.