IDF 2010 With all the song and dance Intel is making about Sandy Bridge, it's hard to miss many of the smaller stories at this years Intel Developer Forum show in San Francisco.

One of these is that Intel managed to get pair of less than 30-day old next-gen Xeon CPUs up and running in time for the show. Codenamed Romley, these CPUs aren't due to be released until sometime in the second half of 2011.

For that reason Intel isn't giving away much info about the specs of Romley, but we've been able to gather the following facts for you: Romley CPUs are based on the new Sandy Bridge architecture, although it hasn't been made clear if it will also have the integrated graphics of the desktop and laptop versions.

Romley CPUs have eight physical cores, plus eight Hyper-Threaded logical cores per CPU, versus the six plus six of the existing Xeon 5600-series. Finally, up to two Romley CPUs can be installed in one motherboard. The existing 5520 chipset will be replaced by a new chipset, codenamed Patsburg, which has native support for SAS 6Gbps drives. There was no word on the chipset's other features though.

Instead of standard, registered ECC DDR3 memory, Romley CPUs use a new form of registered ECC DDR3 known as LRDIMMs (Load Reduced Dual-Inline Memory Modules). This new form of memory has been designed to allow systems with more than 32GB of memory to run each DIMM at its maximum frequency. Standard DDR3 systems cannot do this, as when many DIMMs are installed, the signal strength between the DIMMs and memory controller gets so weak that the frequency has to be lowered to maintain data integrity.

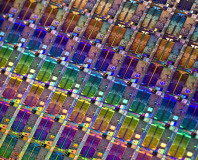

We managed to sneak this picture of a LRDIMM on the Samsung stand at IDF before being shooed away by a distinctly un-PR-trained Samsung employee.

LRDIMMs include an on-board buffer that enhances the signal and tricks the memory controller into thinking only a single DIMM is installed.

Finally, while this hasn't been confirmed by Intel, we suspect that Romley CPUs may have a quad-channel memory controller, rather than the triple-channel controller of current Xeon CPUs. We reckon this is the case, as the Romley demo system had 8GB of RAM installed, a configuration not ideal with triple-channel DIMMs; the Samsung leaflet for its LRDIMMs also had a drawing indicating four DIMMs.

Let us know how you think Romley is shaping up in the forum.

One of these is that Intel managed to get pair of less than 30-day old next-gen Xeon CPUs up and running in time for the show. Codenamed Romley, these CPUs aren't due to be released until sometime in the second half of 2011.

For that reason Intel isn't giving away much info about the specs of Romley, but we've been able to gather the following facts for you: Romley CPUs are based on the new Sandy Bridge architecture, although it hasn't been made clear if it will also have the integrated graphics of the desktop and laptop versions.

Romley CPUs have eight physical cores, plus eight Hyper-Threaded logical cores per CPU, versus the six plus six of the existing Xeon 5600-series. Finally, up to two Romley CPUs can be installed in one motherboard. The existing 5520 chipset will be replaced by a new chipset, codenamed Patsburg, which has native support for SAS 6Gbps drives. There was no word on the chipset's other features though.

Instead of standard, registered ECC DDR3 memory, Romley CPUs use a new form of registered ECC DDR3 known as LRDIMMs (Load Reduced Dual-Inline Memory Modules). This new form of memory has been designed to allow systems with more than 32GB of memory to run each DIMM at its maximum frequency. Standard DDR3 systems cannot do this, as when many DIMMs are installed, the signal strength between the DIMMs and memory controller gets so weak that the frequency has to be lowered to maintain data integrity.

We managed to sneak this picture of a LRDIMM on the Samsung stand at IDF before being shooed away by a distinctly un-PR-trained Samsung employee.

LRDIMMs include an on-board buffer that enhances the signal and tricks the memory controller into thinking only a single DIMM is installed.

Finally, while this hasn't been confirmed by Intel, we suspect that Romley CPUs may have a quad-channel memory controller, rather than the triple-channel controller of current Xeon CPUs. We reckon this is the case, as the Romley demo system had 8GB of RAM installed, a configuration not ideal with triple-channel DIMMs; the Samsung leaflet for its LRDIMMs also had a drawing indicating four DIMMs.

Let us know how you think Romley is shaping up in the forum.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.